Payment Method

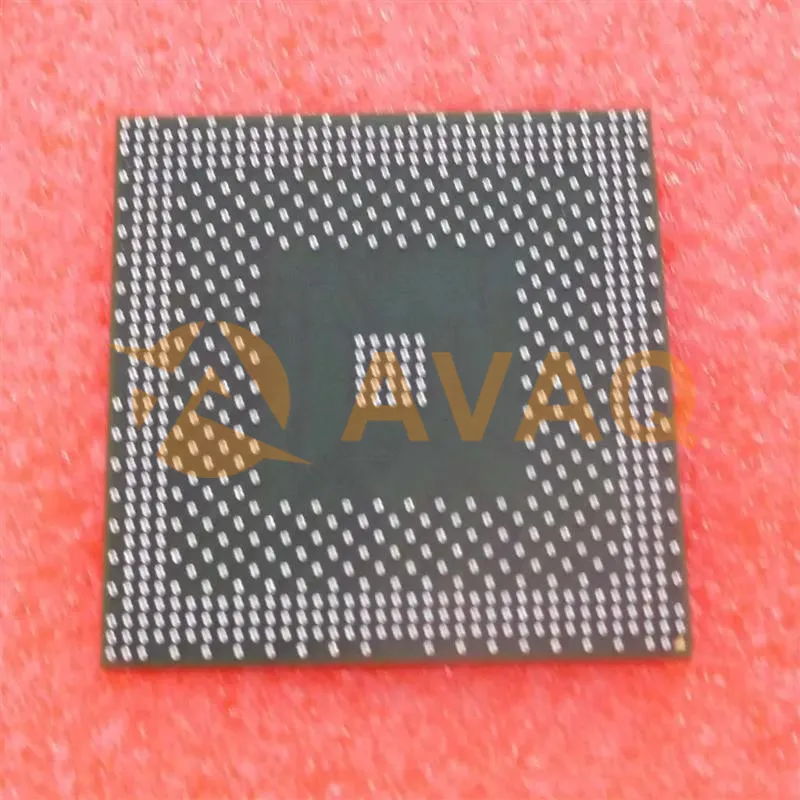

Next-generation memory controller with compact design

BGAManufacturer:

Mfr.Part #:

82845GE

Datasheet:

Part Life Cycle Code:

Active

Reach Compliance Code:

compliant

HTS Code:

8542.31.00.01

JESD-30 Code:

S-PBGA-B478

EDA/CAD Models:

Send all BOMs to ![]() [email protected],

or fill out the form below for a quote on 82845GE. Guaranteed response within

[email protected],

or fill out the form below for a quote on 82845GE. Guaranteed response within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

This datasheet is for both the Intel® 82845GE Graphics and Memory Controller Hub (GMCH) and Intel® 82845PE Memory Controller Hub (MCH) components. The 82845GE GMCH is part of the Intel® 845GE chipset and the 82845PE MCH is part of the Intel® 845PE chipset. Each chipset contains two main components: GMCH (MCH) for the host bridge and I/O Controller Hub for the I/O subsystem. The GMCH (MCH) provides the processor interface, system memory interface, hub interface, and additional interfaces in an 845GE / 845PE chipset desktop platform. Both the 845GE chipset and 845PE chipset use the 82801DB ICH4 for the I/O Controller Hub.

| Part Life Cycle Code | Active | Reach Compliance Code | compliant |

| HTS Code | 8542.31.00.01 | JESD-30 Code | S-PBGA-B478 |

| Number of Terminals | 478 | Power Supplies | 1.5 V |

| Qualification Status | Not Qualified | Supply Voltage-Nom | 1.5 V |

| Surface Mount | YES | Technology | CMOS |

| Terminal Form | BALL | Terminal Pitch | 1 mm |

| Terminal Position | BOTTOM |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.