Payment Method

208-Pin PQFP Tray

208-PQFP (28x28)Manufacturer:

MICROCHIP TECHNOLOGY INC

Mfr.Part #:

A3PE3000L-PQG208I

Datasheet:

Part Life Cycle Code:

Active

Reach Compliance Code:

compliant

HTS Code:

8542.39.00.01

Factory Lead Time:

52 Weeks

EDA/CAD Models:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for A3PE3000L-PQG208I, guaranteed quotes back within

[email protected],

or fill below form to Quote for A3PE3000L-PQG208I, guaranteed quotes back within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

Boasting a cutting-edge architecture based on Microchip Technology's ProASIC3E family, the A3PE3000L-PQG208I FPGA is a powerhouse of innovation tailored for the most demanding requirements. Its on-chip PLLs ensure precise clock management, while its compatibility with Microchip's Libero SoC design software facilitates seamless integration into intricate system designs. Operating at a supply voltage of 1.2V within a commercial temperature range, this FPGA strikes the perfect balance between performance and reliability, setting a new benchmark in field-programmable gate array technology

| Part Life Cycle Code | Active | Reach Compliance Code | compliant |

| HTS Code | 8542.39.00.01 | Factory Lead Time | 52 Weeks |

| JESD-30 Code | S-PQFP-G208 | JESD-609 Code | e3 |

| Length | 28 mm | Moisture Sensitivity Level | 3 |

| Number of CLBs | 75264 | Number of Equivalent Gates | 3000000 |

| Number of Inputs | 147 | Number of Logic Cells | 75264 |

| Number of Outputs | 147 | Number of Terminals | 208 |

| Operating Temperature-Max | 85 °C | Operating Temperature-Min | -40 °C |

| Organization | 75264 CLBS, 3000000 GATES | Peak Reflow Temperature (Cel) | 245 |

| Power Supplies | 1.2/1.5,1.2/3.3 V | Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY |

| Qualification Status | Not Qualified | Seated Height-Max | 4.1 mm |

| Supply Voltage-Max | 1.575 V | Supply Voltage-Min | 1.14 V |

| Supply Voltage-Nom | 1.2 V | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | INDUSTRIAL |

| Terminal Finish | MATTE TIN | Terminal Form | GULL WING |

| Terminal Pitch | 0.5 mm | Terminal Position | QUAD |

| Time@Peak Reflow Temperature-Max (s) | 30 | Width | 28 mm |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

C100

Issi

Video ICs 4MP H.265 Video Processor - 64MB DDR2, BGA85, 5mm x 6mm

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

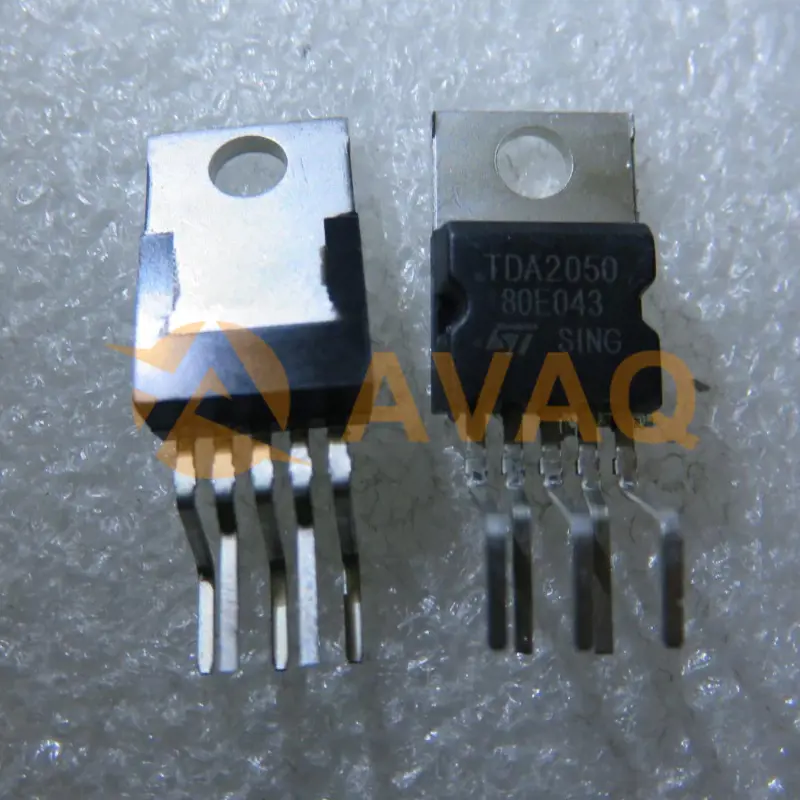

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power