Payment Method

12ns response time on the 512-cell EE PLD with CMOS technology and PQFP208 package

QFP-208Manufacturer:

CYPRESS SEMICONDUCTOR CORP

Mfr.Part #:

CY37512P208-100NI

Datasheet:

Part Life Cycle Code:

Obsolete

Pin Count:

208

Reach Compliance Code:

not_compliant

HTS Code:

8542.39.00.01

EDA/CAD Models:

Send all BOMs to ![]() [email protected],

or fill out the form below for a quote on CY37512P208-100NI. Guaranteed response within

[email protected],

or fill out the form below for a quote on CY37512P208-100NI. Guaranteed response within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

General DescriptionThe Ultra37000™ family of CMOSCPLDs provides a range of high-density programmable logic solutions with unparalleled system performance. The Ultra37000 family is designed to bring the flexibility, ease of use, and performance of the 22V10 to high-density CPLDs. The architecture is based on a number of logic blocks that are connected by a Programmable Interconnect Matrix (PIM).

| Part Life Cycle Code | Obsolete | Pin Count | 208 |

| Reach Compliance Code | not_compliant | HTS Code | 8542.39.00.01 |

| Additional Feature | 512 MACROCELLS; CONFIGURABLE I/O OPERATION WITH 3.3V OR 5V | Architecture | PLA-TYPE |

| Clock Frequency-Max | 80 MHz | In-System Programmable | YES |

| JESD-30 Code | S-PQFP-G208 | JESD-609 Code | e0 |

| JTAG BST | YES | Length | 28 mm |

| Moisture Sensitivity Level | 3 | Number of Dedicated Inputs | 1 |

| Number of I/O Lines | 160 | Number of Inputs | 165 |

| Number of Macro Cells | 512 | Number of Outputs | 160 |

| Number of Terminals | 208 | Operating Temperature-Max | 85 °C |

| Operating Temperature-Min | -40 °C | Organization | 1 DEDICATED INPUTS, 160 I/O |

| Output Function | MACROCELL | Power Supplies | 3.3/5 V |

| Programmable Logic Type | EE PLD | Propagation Delay | 12 ns |

| Qualification Status | Not Qualified | Seated Height-Max | 3.7 mm |

| Supply Voltage-Max | 5.5 V | Supply Voltage-Min | 4.5 V |

| Supply Voltage-Nom | 5 V | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | INDUSTRIAL |

| Terminal Finish | TIN LEAD | Terminal Form | GULL WING |

| Terminal Pitch | 0.5 mm | Terminal Position | QUAD |

| Width | 28 mm |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

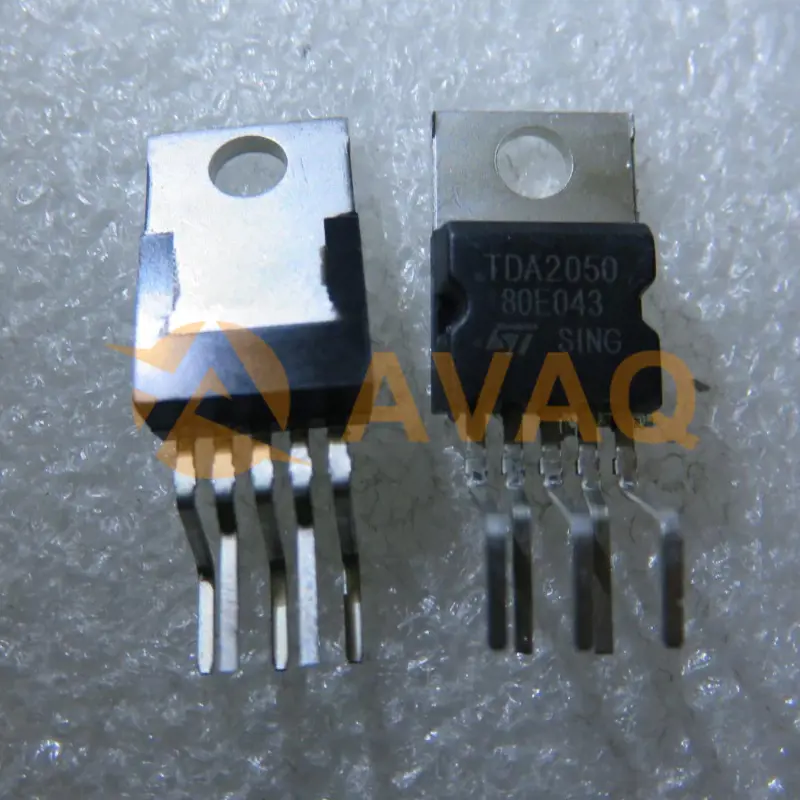

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power

DS1307+

Analog Devices

I2C DIP-8 Real-time Clocks (RTC) ROHS