Payment Method

RF IC Demodulator AM, FM 52MHz 84-PLCC (29.31x29.31)

PLCC84Manufacturer:

Mfr.Part #:

HSP50210JI-52Z

Datasheet:

Number Of Pins:

84

Frequency:

52 MHz

Max Operating Temperature:

85 °C

Max Supply Voltage:

5.25 V

EDA/CAD Models:

Send all BOMs to ![]() [email protected],

or fill out the form below for a quote on HSP50210JI-52Z. Guaranteed response within

[email protected],

or fill out the form below for a quote on HSP50210JI-52Z. Guaranteed response within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

Support is limited to customers who have already adopted these products.

The Digital Costas Loop (DCL) performs many of the baseband processing tasks required for the demodulation of BPSK, QPSK, 8-PSK, OQPSK, FSK, AM and FM waveforms. These tasks include matched filtering, carrier tracking, symbol synchronization, AGC, and soft decision slicing. The DCL is designed for use with the HSP50110 Digital Quadrature Tuner to provide a two chip solution for digital down conversion and demodulation. The DCL processes the In-phase (I) and quadrature (Q) components of a baseband signal which have been digitized to 10 bits. As shown in the block diagram, the main signal path consists of a complex multiplier, selectable matched filters, gain multipliers, cartesian-to-polar converter, and soft decision slicer. The complex multiplier mixes the I and Q inputs with the output of a quadrature NCO. Following the mix function, selectable matched filters are provided which perform integrate and dump or root raised cosine filtering (a ~ 0. 40). The matched filter output is routed to the slicer, which generates 3-bit soft decisions, and to the cartesian-topolar converter, which generates the magnitude and phase terms required by the AGC and Carrier Tracking Loops. The PLL system solution is completed by the HSP50210 error detectors and second order Loop Filters that provide carrier tracking and symbol synchronization signals. In applications where the DCL is used with the HSP50110, these control loops are closed through a serial interface between the two parts. To maintain the demodulator performance with varying signal power and SNR, an internal AGC loop is provided to establish an optimal signal level at the input to the slicer and to the cartesian-to-polar converter.

| Number of Pins | 84 | Frequency | 52 MHz |

| Max Operating Temperature | 85 °C | Max Supply Voltage | 5.25 V |

| Min Operating Temperature | -40 °C | Min Supply Voltage | 4.75 V |

| Operating Supply Current | 500 µA | Operating Supply Voltage | 5 V |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | $161.237 | $161.24 |

| 200+ | $64.336 | $12,867.20 |

| 500+ | $62.185 | $31,092.50 |

| 1000+ | $61.123 | $61,123.00 |

The prices below are for reference only.

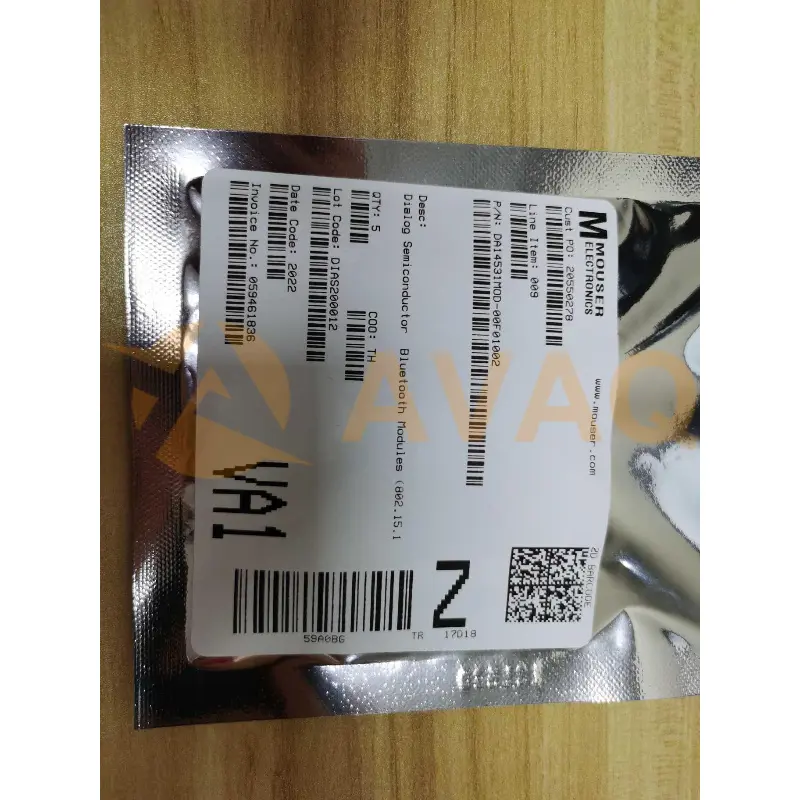

DA14531MOD-00F01002

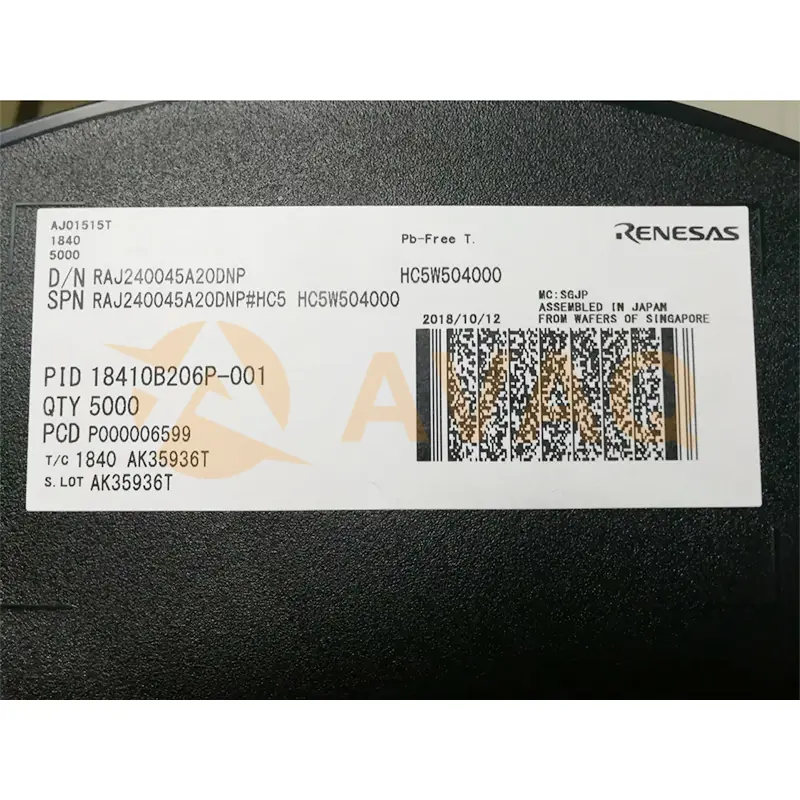

Renesas Technology Corp

1000+ $1.268

DA16200MOD-AAC4WA32

Renesas Technology Corp

802.11b/g/n 2.4Gbps 2.4GHz CCK/DSSS/OFDM T/R

HD10551

Renesas Technology Corp

Prescaler for Digital Tuning System

UPB1507GV

Renesas Technology Corp

8-pin PDSO package

uPB1507GV-E1

Renesas Technology Corp

Pulse-perfect performance: UPB15 SERIES Prescaler for precise timing control