Payment Method

Counter IC Divide-by-N 1 Element 5 Bit Positive Edge 16-CDIP

16-CDIP(0.300",7.62mm)Manufacturer:

Texas Instruments

Mfr.Part #:

JM38510/05652BEA

Datasheet:

Series:

4000B

Logic Type:

Divide-by-N

Direction:

Up

Number Of Elements:

1

EDA/CAD Models:

Send all BOMs to ![]() [email protected],

or fill out the form below for a quote on JM38510/05652BEA. Guaranteed response within

[email protected],

or fill out the form below for a quote on JM38510/05652BEA. Guaranteed response within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

CD4018B types consist of 5 Johnson-Counter stages, buffered Q outputs from each stage, and counter preset control gating. CLOCK, RESET, DATA, PRESET ENABLE, and 5 individual JAM inputs are provided. Divide by 10, 8, 6, 4, or 2 counter configurations can be implemented by feeding the Q\5, Q\4, Q\3, Q\2, Q\1 signals, respectively, back to the DATA input. Divide-by-9, 7, 5, or 3 counter configurations can be implemented by the use of a CD4011B to gate the feedback connection to the DATA input. Divide-by functions grater than 10 can be achieved by use of multiple CD4018B units. The counter is advanced one count at the positive clock-signal transition Schmitt Trigger action on the clock line permits unlimited clock rise and fall times. A high RESET signal clear the counter to an all-zero condition. A high PRESET-ENABLE signal allows information on the JAM inputs to preset the counter. Anti-lock gating is provided to assure the proper counting sequence.

The CD4018B types are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix), 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (M, M96, MT, and NSR suffixes), and 16-lead thin shrink small-outline packages (PW and PWR suffixes).

| Series | 4000B | Logic Type | Divide-by-N |

| Direction | Up | Number of Elements | 1 |

| Number of Bits per Element | 5 | Reset | Asynchronous |

| Timing | Synchronous | Count Rate | 17 MHz |

| Trigger Type | Positive Edge | Voltage - Supply | 3 V ~ 18 V |

| Operating Temperature | -55°C ~ 125°C (TA) | Mounting Type | Through Hole |

| Base Product Number | JM38510 |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

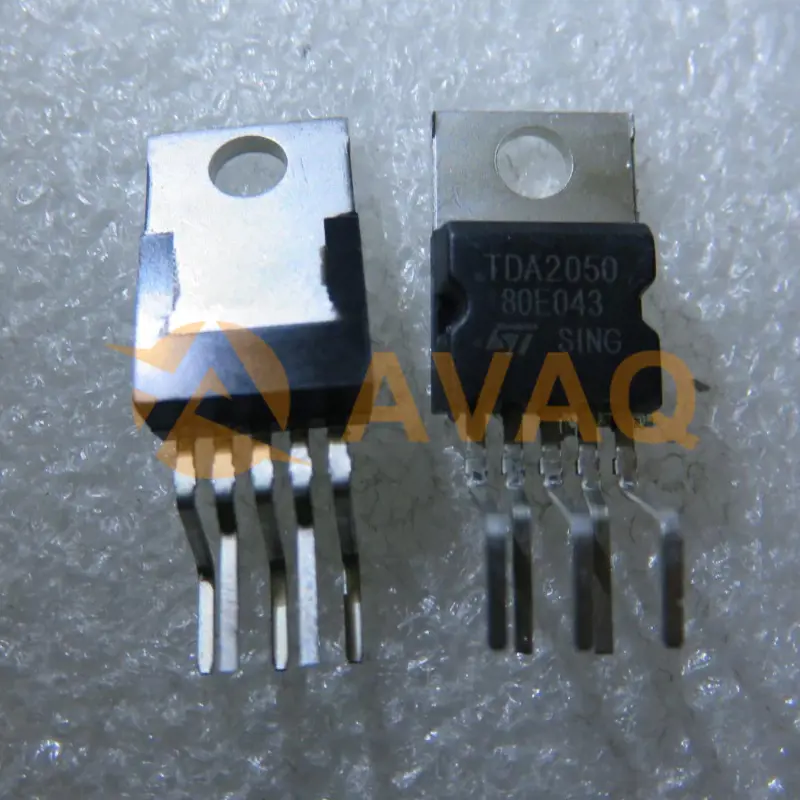

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power

DS1307+

Analog Devices

I2C DIP-8 Real-time Clocks (RTC) ROHS