Payment Method

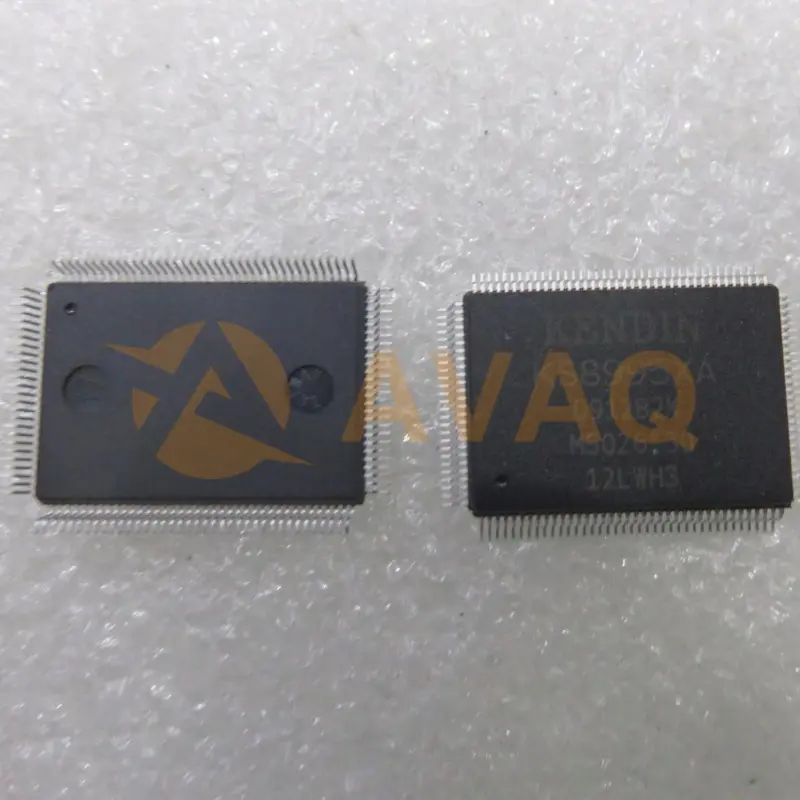

Ethernet LAN switching circuit featuring CMOS technology and a PQFP128 plastic package for enhanced durability

128-PQFP (14x20)Manufacturer:

Mfr.Part #:

KS8995XA

Datasheet:

Pbfree Code:

No

Part Life Cycle Code:

Obsolete

Pin Count:

128

Reach Compliance Code:

not_compliant

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

In terms of management, the KS8995XA offers various interfaces including a serial interface and an MDIO interface for easy configuration and monitoring. This makes it simple for network administrators to keep tabs on network activity and make any necessary adjustments. With built-in diagnostic tools, troubleshooting network issues is a breeze, ensuring minimal downtime and maximum efficiency

| Source Content uid | KS8995XA | Pbfree Code | No |

| Part Life Cycle Code | Obsolete | Pin Count | 128 |

| Reach Compliance Code | not_compliant | HTS Code | 8542.39.00.01 |

| JESD-30 Code | R-PQFP-G128 | JESD-609 Code | e0 |

| Length | 20 mm | Moisture Sensitivity Level | 3 |

| Number of Functions | 1 | Number of Terminals | 128 |

| Operating Temperature-Max | 70 °C | Operating Temperature-Min | |

| Peak Reflow Temperature (Cel) | 240 | Qualification Status | Not Qualified |

| Seated Height-Max | 3.4 mm | Supply Voltage-Nom | 1.8 V |

| Surface Mount | YES | Technology | CMOS |

| Telecom IC Type | LAN SWITCHING CIRCUIT | Temperature Grade | COMMERCIAL |

| Terminal Finish | Tin/Lead (Sn85Pb15) | Terminal Form | GULL WING |

| Terminal Pitch | 0.5 mm | Terminal Position | QUAD |

| Time@Peak Reflow Temperature-Max (s) | 30 | Width | 14 mm |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for KS8995XA, guaranteed quotes back within

[email protected],

or fill below form to Quote for KS8995XA, guaranteed quotes back within

![]() 12hr.

12hr.