Payment Method

Layerscape 64-bit Arm Cortex-A53, Single-core, 600MHz, 0 to 105C, Security enabled

211-VFLGAManufacturer:

Mfr.Part #:

LS1012ASE7EKA

Datasheet:

Silicon Rev:

Rev 1

Family:

QorIQ LS1012A

Qualification Tier:

Industrial

UART:

10

EDA/CAD Models:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for LS1012ASE7EKA, guaranteed quotes back within

[email protected],

or fill below form to Quote for LS1012ASE7EKA, guaranteed quotes back within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

Microprocessors - MPU Layerscape 64-bit Arm Cortex-A53, Single-core, 600MHz, 0 to 105C, Security enabled

| Silicon Rev | Rev 1 | Family | QorIQ LS1012A |

| Qualification tier | Industrial | UART | 10 |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

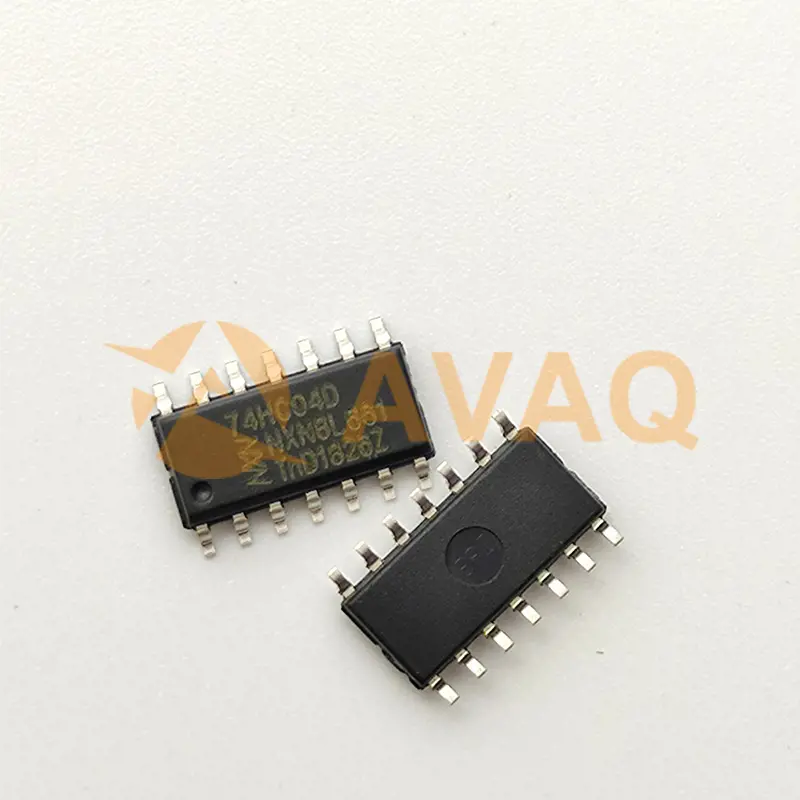

74HC04D

Toshiba

5000+ $0.072

TDA8947J

NXP

Audio Amplifiers 3/4 CHANNEL AUDIO AMPLIFIER

TDA8920BJ

Nxp

Experience crystal-clear sound quality and robust power handling with this efficient Class D amplifier

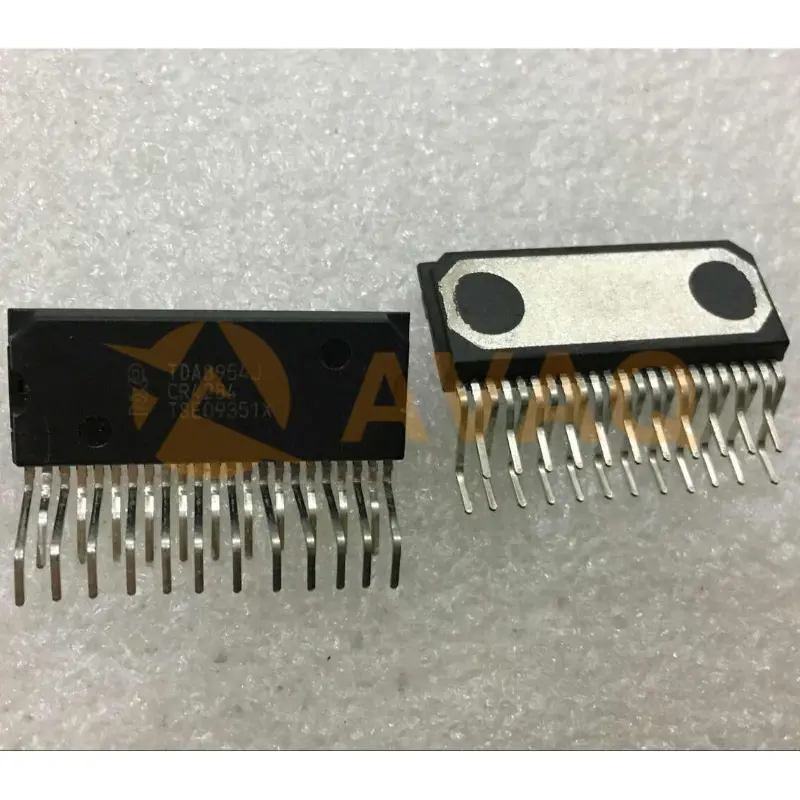

TDA8954J

Nxp

Plastic SOT411-1 PZFM23 audio amplifier

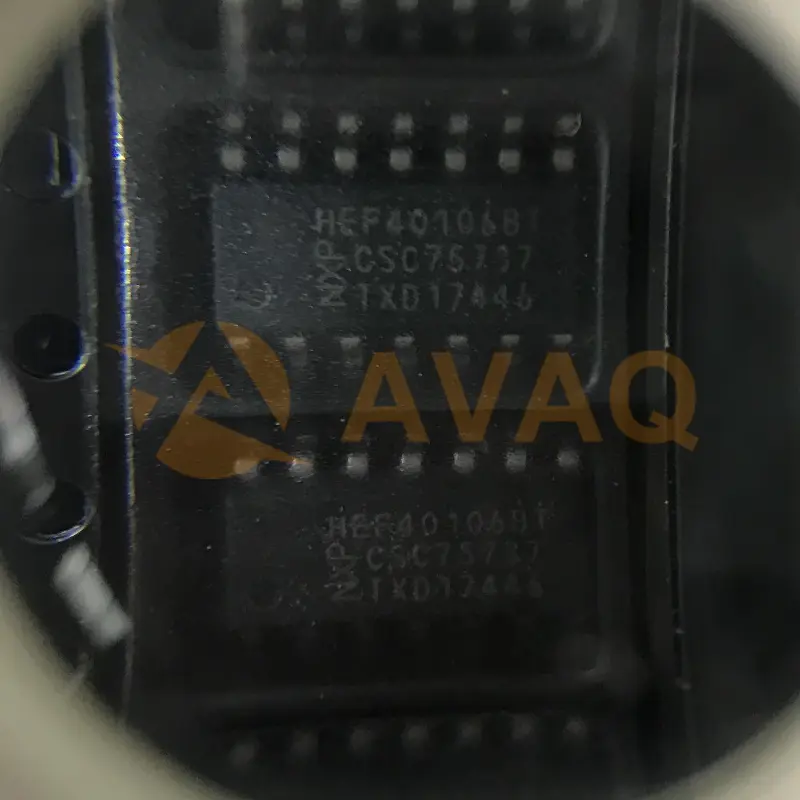

HEF40106BT

Nexperia

Inverter Schmitt Trigger 6-Element CMOS 14-Pin SO