Payment Method

High-performance CMOS technology

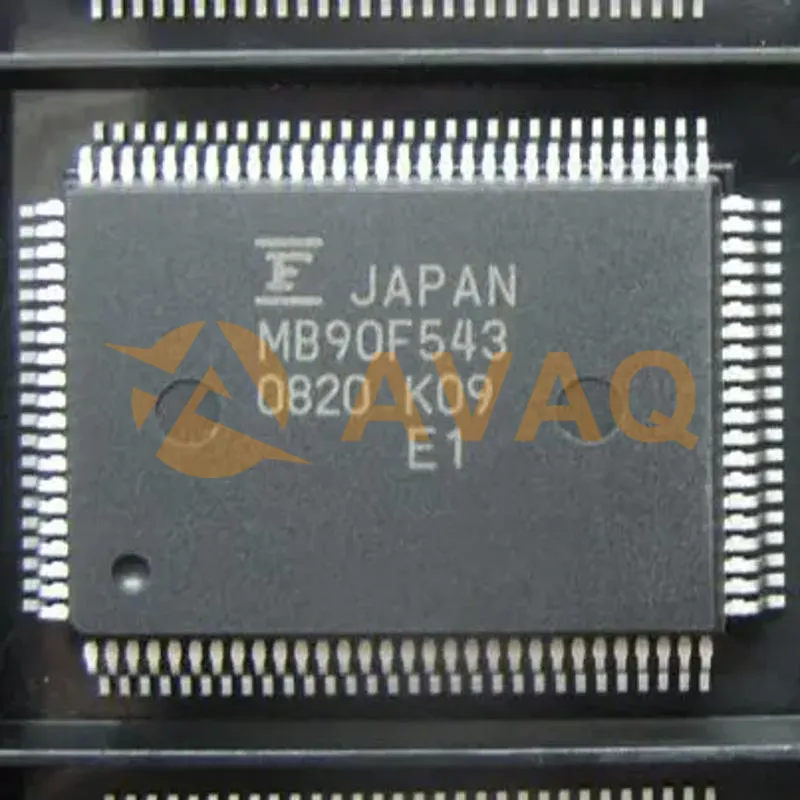

QFP-100Manufacturer:

CYPRESS SEMICONDUCTOR CORP

Mfr.Part #:

MB90F543PF

Datasheet:

Part Life Cycle Code:

Obsolete

Reach Compliance Code:

compliant

HTS Code:

8542.31.00.01

Has ADC:

YES

EDA/CAD Models:

Send all BOMs to ![]() [email protected],

or fill out the form below for a quote on MB90F543PF. Guaranteed response within

[email protected],

or fill out the form below for a quote on MB90F543PF. Guaranteed response within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

■ DESCRIPTIONThe MB90540/545 series with FULL-CAN*1 and FLASH ROM is specially designed for automotive and industrial applications. Its main features are two on board CAN Interfaces (one for MB90V545 series) , which conform to V2.0 Part A and Part B, supporting very flexible message buffer scheme and so offering more functions than a normal full CAN approach. The instruction set by F2MC-16LX CPU core inherits an AT architecture of the F2MC*2 family with additional instruction sets for high-level languages, extended addressing mode, enhanced multiplication/division instructions, and enhanced bit manipulation instructions.The micro controller has a 32-bit accumulator for processing long word data.The MB90540/545 series has peripheral resources of 8/10-bit A/D converters, UART (SCI) , extended I/O serial interfaces, 8/16-bit timer, I/O timer (input capture (ICU) , output compare (OCU)).■ FEATURES• Clock Embedded PLL clock multiplication circuit Operating clock (PLL clock) can be selected from : divided-by-2 of oscillation or one to four times the oscillation Minimum instruction execution time : 62.5 ns (operation at oscillation of 4 MHz, four times the oscillation clock) Subsystem Clock : 32 kHz• Instruction set to optimize controller applications Rich data types (bit, byte, word, long word) Rich addressing mode (23 types) Enhanced signed multiplication/division instruction and RETI instruction functions Enhanced precision calculation realized by the 32-bit accumulator• Instruction set designed for high level language (C language) and multi-task operations Adoption of system stack pointer Enhanced pointer indirect instructions Barrel shift instructions• Program patch function (for two address pointers)• Enhanced execution speed : 4-byte Instruction queue• Enhanced interrupt function : 8 levels, 34 factors• Automatic data transmission function independent of CPU operation Extended intelligent I/O service function (EI2OS)• Embedded ROM size and types Mask ROM : 256 Kbytes / 64 Kbytes / 128 Kbytes Flash ROM : 128 Kbytes/256 Kbytes Embedded RAM size : 2 Kbytes/4 Kbytes/6 Kbytes/8 Kbytes (evaluation chip)• Flash ROM Supports automatic programming, Embedded Algorithm TM* Write/Erase/Erase-Suspend/Resume commands A flag indicating completion of the algorithm Hard-wired reset vector available in order to point to a fixed boot sector in Flash Memory Erase can be performed on each block Block protection with external programming voltage• Low-power consumption (stand-by) mode Sleep mode (mode in which CPU operating clock is stopped) Stop mode (mode in which oscillation is stopped) CPU intermittent operation mode Clock mode Hardware stand-by mode• Process 0.5 µm CMOS technology• I/O port General-purpose I/O ports : 81 ports• Timer Watchdog timer : 1 channel 8/16-bit PPG timer : 8/16-bit × 4 channels 16-bit re-load timer : 2 channels• 16-bit I/O timer 16-bit free-run timer : 1 channel Input capture : 8 channels Output compare : 4 channels• Extended I/O serial interface : 1 channel• UART 0 With full-duplex double buffer (8-bit length) Clock asynchronized or clock synchronized (with start/stop bit) transmission can be selectively used.• UART 1 With full-duplex double buffer (8-bit length) Clock asynchronized or clock synchronized serial (extended I/O serial) can be used.• External interrupt circuit (8 channels) A module for starting an extended intelligent I/O service (EI2OS) and generating an external interrupt which is triggered by an external input.• Delayed interrupt generation module Generates an interrupt request for switching tasks.• 8/10-bit A/D converter (8 channels) 8/10-bit resolution can be selectively used. Starting by an external trigger input. Conversion time : 26.3 µs• FULL-CAN interfaces MB90540 series : 2 channel MB90545 series : 1 channel Conforming to Version 2.0 Part A and Part B Flexible message buffering (mailbox and FIFO buffering can be mixed)• External bus interface : Maximum address space 16 Mbytes• Package: QFP-100, LQFP-100

| Part Life Cycle Code | Obsolete | Reach Compliance Code | compliant |

| HTS Code | 8542.31.00.01 | Has ADC | YES |

| Address Bus Width | 24 | Bit Size | 16 |

| Clock Frequency-Max | 16 MHz | DAC Channels | NO |

| DMA Channels | NO | External Data Bus Width | 16 |

| JESD-30 Code | R-PQFP-G100 | JESD-609 Code | e0 |

| Length | 20 mm | Number of I/O Lines | 81 |

| Number of Terminals | 100 | Operating Temperature-Max | 85 °C |

| Operating Temperature-Min | -40 °C | PWM Channels | NO |

| Peak Reflow Temperature (Cel) | NOT SPECIFIED | Qualification Status | Not Qualified |

| ROM Programmability | FLASH | Seated Height-Max | 3.35 mm |

| Speed | 16 MHz | Supply Voltage-Max | 5.5 V |

| Supply Voltage-Min | 4.5 V | Supply Voltage-Nom | 5 V |

| Surface Mount | YES | Technology | CMOS |

| Temperature Grade | INDUSTRIAL | Terminal Finish | TIN LEAD |

| Terminal Form | GULL WING | Terminal Pitch | 0.65 mm |

| Terminal Position | QUAD | Time@Peak Reflow Temperature-Max (s) | NOT SPECIFIED |

| Width | 14 mm | uPs/uCs/Peripheral ICs Type | MICROCONTROLLER |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

C100

Issi

Video ICs 4MP H.265 Video Processor - 64MB DDR2, BGA85, 5mm x 6mm

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

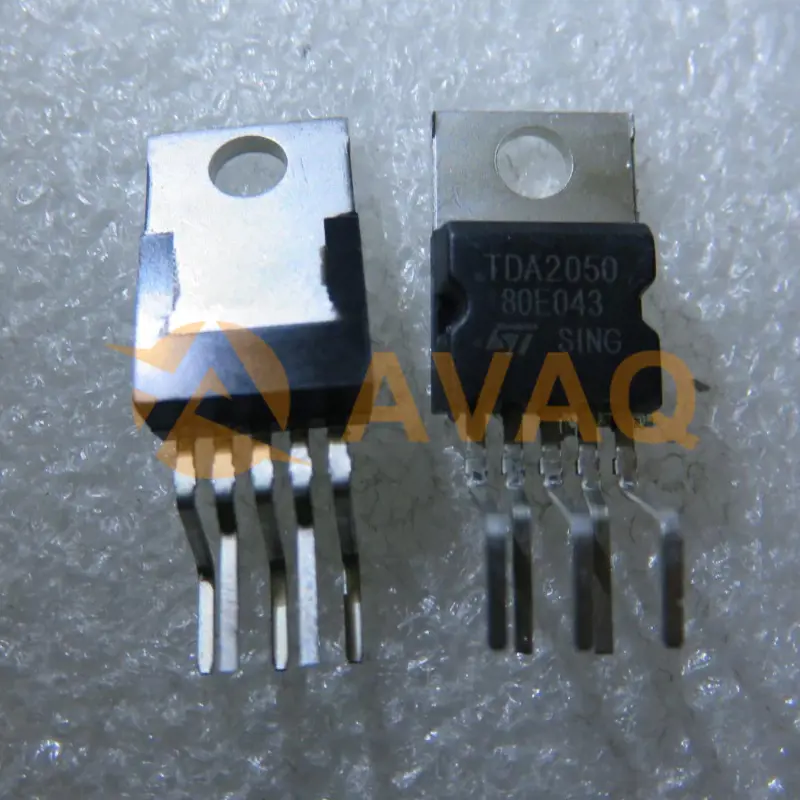

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power