Payment Method

LowPowerIntegratedMultiprotocolProcessorReferenceManual

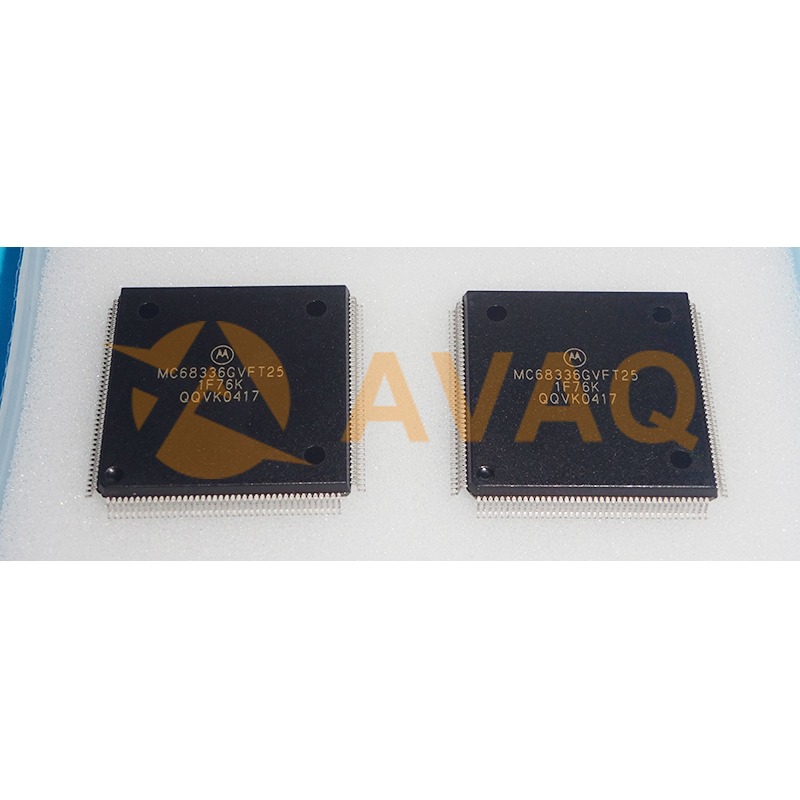

QFPManufacturer:

Mfr.Part #:

MC68LC302

Datasheet:

Package/Case:

QFP

EDA/CAD Models:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for MC68LC302, guaranteed quotes back within

[email protected],

or fill below form to Quote for MC68LC302, guaranteed quotes back within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

INTRODUCTIONMotorola has developed a low-cost version of the well-known MC68302 integrated multiprotocol processor (IMP) called the MC68LC302. Simply put, the LC302 is a traditional 68302 minus the third serial communication controller (SCC3) and has a new static 68000 core, a new timer and low power modes. It is packaged in a low profile 100 TQFP that reduces board space from the regular 68302, as well as making it suitable for use in height restricted applications such as PCMCIA.FEATURESThe features of the LC302 are as follows. The items in bold face type show major differences from the MC68302, although a complete list of differences is given in 1.4 LC302 Differences. • On-Chip Static 68000 Core Supporting a 16- or 8-Bit M68000 Family-System • SIB Including: Independent Direct Memory Access (IDMA) Controller. Interrupt Controller with Two Modes of Operation Parallel Input/Output (I/O) Ports, some with Interrupt Capability Parallel Input/Output (I/O) Ports on D15-D8 in 8 bit mode On-Chip 1152-Byte Dual-Port RAM Three Timers Including a Watchdog Timer New Periodic Interrupt Timer (PIT) Four Programmable Chip-Select Lines with Wait-State Generator Logic Programmable Address Mapping of the Dual-Port RAM and IMP Registers On-Chip Clock Generator with Output Signal On-Chip PLL Allows Operation with 32kHz or 4MHz Crystals Glueless Interface to EPROM, SRAM, Flash EPROM, and EEPROM Allows Boot in 8-bit Mode, and Running Switch to 16-bit Mode System Control: System Status and Control Logic Disable CPU Logic (Slave Mode Operation) Hardware Watchdog New Low-Power (Standby) Modes With Wake-up From 2 Pins or PIT Freeze Control for Debugging (Available Only in the PGA Package) DRAM Refresh Controller • CP Including: Main Controller (RISC Processor) Two Independent Full-Duplex Serial Communications Controllers (SCCs) Supporting Various Protocols: High-Level/Synchronous Data Link Control (HDLC/SDLC) Universal Asynchronous Receiver Transmitter (UART) Binary Synchronous Communication (BISYNC) Transparent Modes Autobaud Support Instead of DDCMP and V.110 Boot from SCC Capability Four Serial DMA Channels for the Two SCCs Flexible Physical Interface Accessible by SCCs Including: Motorola Interchip Digital Link (IDL) General Circuit Interface (GCI, Also Known as IOM1-2) Pulse Code Modulation (PCM) Highway Interface Nonmultiplexed Serial Interface (NMSI) Implementing Standard Modem Signals SCP for Synchronous Communication Two Serial Management Controllers (SMCs) To Support IDL and GCI Auxiliary Channels • 100 Pin Thin Quad Flat Pack (TQFP) Packaging

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.