Payment Method

Featuring 3K gates and a 52-pin PLCC package, the PSD813F2A-90J is a high-performance CPLD suitable for diverse circuit design needs

PLCC-52Manufacturer:

STMicroelectronics

Mfr.Part #:

PSD813F2A-90J

Datasheet:

Maximum Operating Frequency:

43.48 MHz

Operating Supply Voltage:

5 V

Minimum Operating Temperature:

0 C

Maximum Operating Temperature:

+ 70 C

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

The PSD813F2A-90J is a versatile and feature-rich system management IC, perfect for addressing the power supply sequencing and monitoring needs of modern digital systems. With its two independent voltage monitoring channels, configurable power-up and power-down sequencing, and wide operating voltage range, it offers a comprehensive solution for ensuring stable and reliable power delivery in a variety of applications. Its programmable undervoltage and overvoltage thresholds, along with the watchdog timer, provide the flexibility and adaptability necessary for effective system monitoring

| Product Category | FPGA - Configuration Memory | Maximum Operating Frequency | 43.48 MHz |

| Operating Supply Voltage | 5 V | Minimum Operating Temperature | 0 C |

| Maximum Operating Temperature | + 70 C | Mounting Style | SMD/SMT |

| Moisture Sensitive | Yes | Product Type | FPGA - Configuration Memory |

| Series | PSD813F2 | Factory Pack Quantity | 500 |

| Subcategory | Programmable Logic ICs | Supply Voltage - Max | 5.5 V |

| Supply Voltage - Min | 4.5 V | Unit Weight | 0.104503 oz |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for PSD813F2A-90J, guaranteed quotes back within

[email protected],

or fill below form to Quote for PSD813F2A-90J, guaranteed quotes back within

![]() 12hr.

12hr.

HX711

Avia Semicon (Xiamen)

Precise analog-to-digital conversion for industrial and scientific application

ADS1115

Texas Instruments

Accurate measurement made easy with -bit A/D conversio

PIC16F628A

Microchip

Latest PICF version features enhanced analog capabilities

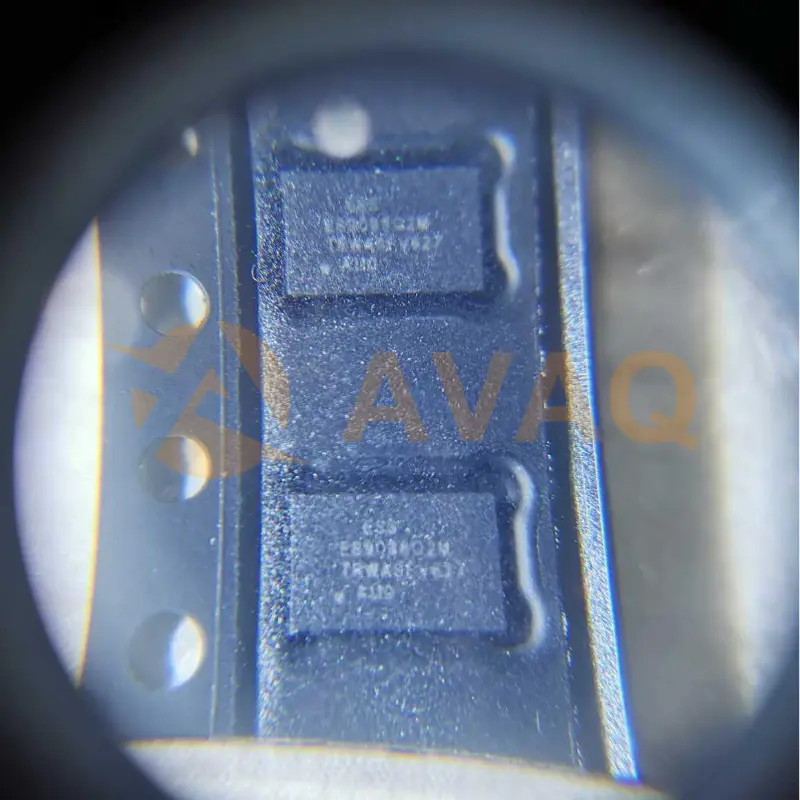

ES9038Q2M

ESS TECHNOLOGY

High-resolution digital audio processing for crystal-clear clarit

ES9018K2M

Ess Technology

Premium Sabre 32 Reference DAC providing superior audio clarity and detail