Payment Method

MPU MPC8XX 50MHz IC with 256 Ball Grid Array

256-BGAManufacturer:

NXP USA Inc.

Mfr.Part #:

XPC850DEZT50BU

Datasheet:

Series:

MPC8xx

Core Processor:

MPC8xx

Number Of Cores/Bus Width:

1 Core, 32-Bit

Speed:

50MHz

EDA/CAD Models:

Send all BOMs to ![]() [email protected],

or fill out the form below for a quote on XPC850DEZT50BU. Guaranteed response within

[email protected],

or fill out the form below for a quote on XPC850DEZT50BU. Guaranteed response within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

NXP Semiconductors presents the XPC850DEZT50BU microcontroller, a powerful member of the XPC850 family designed to address the demanding requirements of industrial and automotive applications. With its PowerPC core operating at a maximum frequency of 50 MHz and on-chip cache memory, this microcontroller delivers enhanced processing power and efficiency. Its comprehensive set of communication interfaces, including CAN, UART, I2C, and SPI, provides flexible connectivity options for interfacing with different systems and devices. Additionally, the XPC850DEZT50BU is equipped with a diverse range of peripherals such as timers, GPIOs, and analog-to-digital converters, facilitating seamless integration with external devices and sensors. The inclusion of a memory management unit (MMU) ensures efficient memory access and protection, while built-in support for real-time operating systems (RTOS) further enhances its performance in real-time applications

| Series | MPC8xx | Core Processor | MPC8xx |

| Number of Cores/Bus Width | 1 Core, 32-Bit | Speed | 50MHz |

| Co-Processors/DSP | Communications; CPM | RAM Controllers | DRAM |

| Graphics Acceleration | No | Display & Interface Controllers | - |

| Ethernet | 10Mbps (1) | SATA | - |

| USB | USB 1.x (1) | Voltage - I/O | 3.3V |

| Operating Temperature | 0°C ~ 95°C (TA) | Security Features | - |

| Mounting Type | Surface Mount | Additional Interfaces | HDLC/SDLC, I²C, IrDA, PCMCIA-ATA, TDM, UART/USART |

| Base Product Number | XPC85 |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

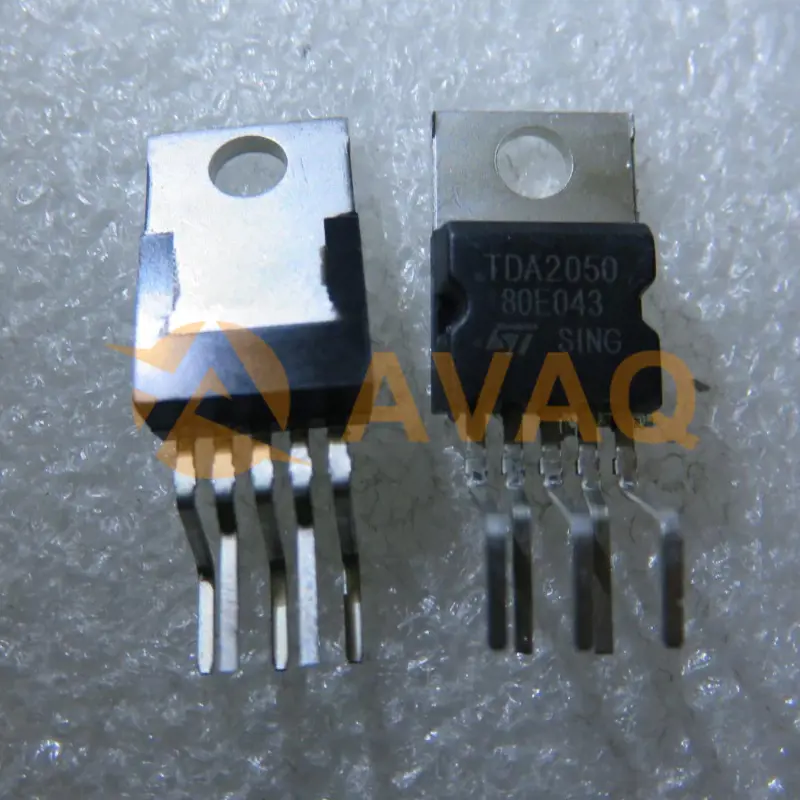

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power

DS1307+

Analog Devices

I2C DIP-8 Real-time Clocks (RTC) ROHS