Payment Method

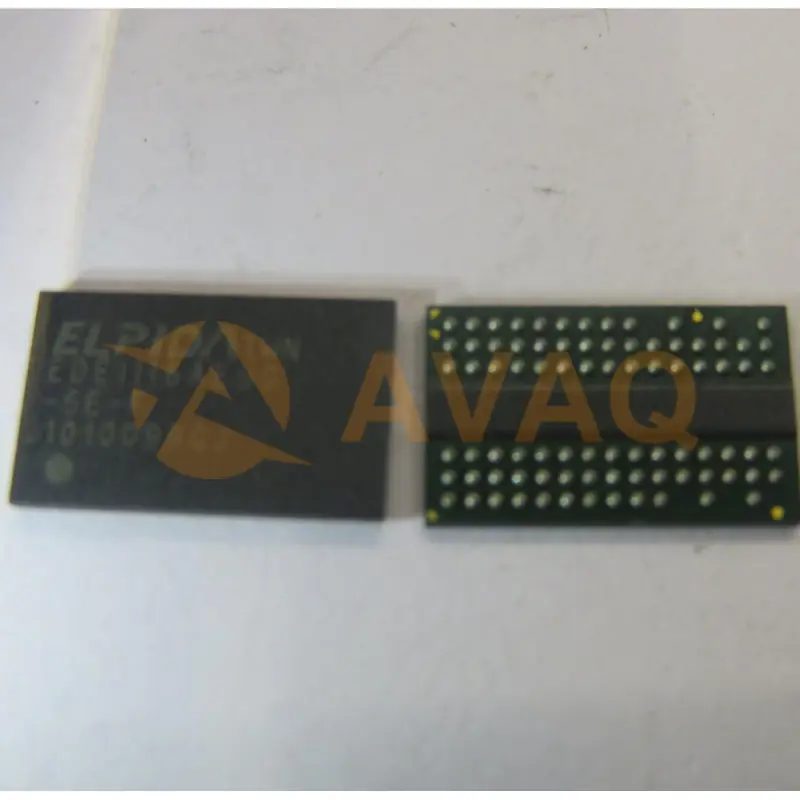

DDR DRAM, 64MX16, 0.45ns, CMOS, PBGA84, HALOGEN FREE AND ROHS COMPLIANT, FBGA-84

BGAManufacturer:

ELPIDA

Mfr.Part #:

EDE1116AEBG-6E-F

Datasheet:

Package/Case:

BGA

Product Type:

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

Double-data-rate architecture; two data transfers per clock cycle

The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

DQS is edge-aligned with data for READs; center aligned with data for WRITEs

Differential clock inputs (CK and /CK)

DLL aligns DQ and DQS transitions with CK transitions

Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

Data mask (DM) for write data

Posted /CAS by programmable additive latency for better command and data bus efficiency

Programmable RDQS, /RDQS output for making 8 organization compatible to 4 organization

/DQS, (/RDQS) can be disabled for single-ended Data Strobe operation

Off-Chip Driver (OCD) impedance adjustment is not supported.

| Product Category | Memory ICs |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for EDE1116AEBG-6E-F, guaranteed quotes back within

[email protected],

or fill below form to Quote for EDE1116AEBG-6E-F, guaranteed quotes back within

![]() 12hr.

12hr.