Payment Method

Synchronous Ethernet and IEEE compliant for reliable transmissio

BGA-144Manufacturer:

Microchip Technology

Mfr.Part #:

ZL30364GDG2

Datasheet:

Programmabe:

Not Verified

PLL:

Yes

Main Purpose:

Ethernet, Fibre Channel, SONET/SDH, Stratum

Input:

Clock

EDA/CAD Models:

Send all BOMs to ![]() [email protected],

or fill out the form below for a quote on ZL30364GDG2. Guaranteed response within

[email protected],

or fill out the form below for a quote on ZL30364GDG2. Guaranteed response within

![]() 12hr.

12hr.

Please fill in the short form below and we will provide you the quotation immediately.

The ZL30364GDG2 is a cutting-edge clock generator and jitter attenuator IC designed for high-speed communication applications. Its advanced features include integrated digital PLLs for on-the-fly frequency changes and fast lock times, as well as programmable output skew and phase adjustment capabilities for precise timing alignment within the system. With its ability to generate multiple output clocks with low jitter and phase noise, this device is perfect for applications that require accurate timing synchronization

| Programmabe | Not Verified | PLL | Yes |

| Main Purpose | Ethernet, Fibre Channel, SONET/SDH, Stratum | Input | Clock |

| Output | LVCMOS, LVPECL | Number of Circuits | 1 |

| Ratio - Input:Output | 11:16 | Differential - Input:Output | Yes/Yes |

| Frequency - Max | 750MHz | Operating Temperature | -40°C ~ 85°C |

| Mounting Type | Surface Mount | Base Product Number | ZL30364 |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

AK1573

Asahi Kasei Microdevices/AKM

1000+ $2.489

MN3102

Panasonic

Durable Plastic Package for Moisture-Sensitive Environments

SI5351A-B-GT

Skyworks

Clock Generator Si5351A-B-GT PK

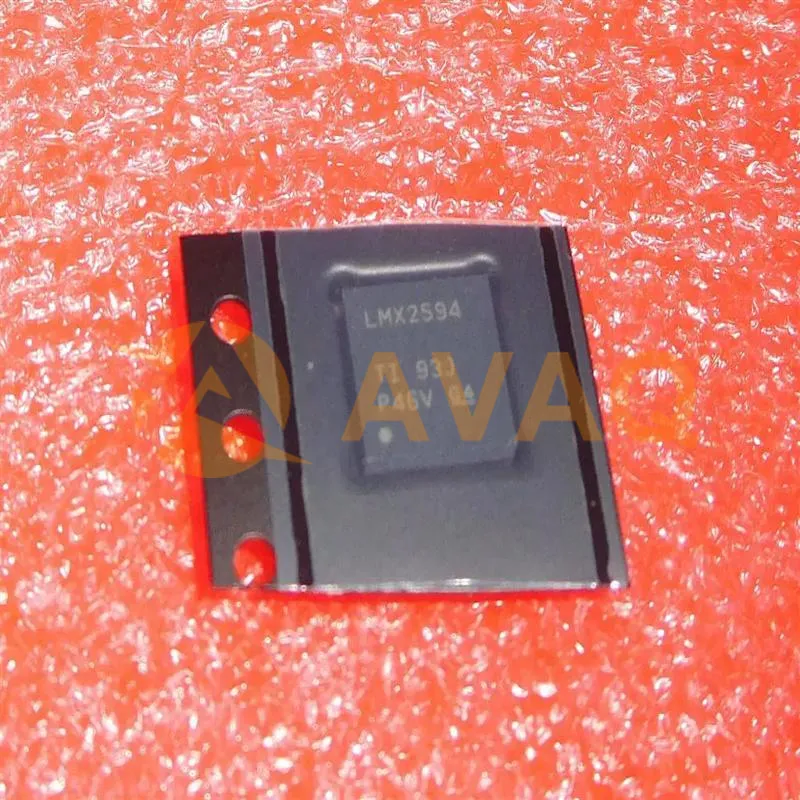

LMX2594RHAT

Texas Instruments

15-GHz wideband PLLatinum™ RF synthesizer with phase synchronization and JESD204B support 40-VQFN -40 to 85"

LM565CN

Texas Instruments

PLL Single 0.25MHz to 0.5MHz 14-Pin MDIP Rail